艾爾西獨家講解振蕩器的應用技巧及注意事項

艾爾西獨家講解振蕩器的應用技巧及注意事項

如何正確了解石英晶體振蕩器,如何運用振蕩器,想必大多數人都會存有疑惑;本文正是就石英晶體振蕩器的應用技巧進行介紹,并且其中還摻雜有在應用過程中的注意事項以及相關專業性知識解釋,想要一解疑惑的朋友可以進來看一看.這篇文章是由美國艾爾西晶振公司發出的,覺得相當有討論價值,與諸位共勉.

振蕩器是產生連續輸出信號的電路.因此它被稱為信號發生器.當產生的信號是振幅和頻率恒定的正弦波時,該振蕩器電路稱為正弦波發生器.該振蕩器可以產生數字邏輯系列(如TTL,CMOS或ECL/PECL)中的方波信號.

振蕩器可以分為三個確定的部分:

①放大器.

②反饋連接.

③頻率確定組件.

④振蕩要求

如果電路有兩個最低要求,石英晶振將振蕩:

①正反饋

②環路增益大于1

當我們將放大器的輸出連接到其輸入時,會提供反饋.如果反饋的輸出與輸入”異相”,則電路具有負反饋(NFB).如果來自輸出的反饋與輸入同相,則電路具有正反饋(PFB).

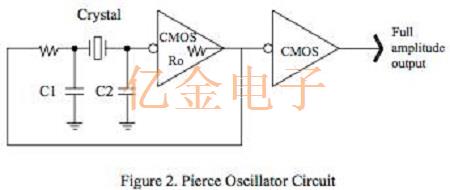

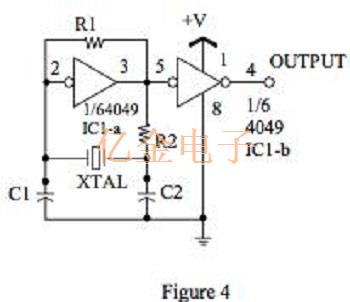

皮爾斯振蕩器電路

優點:

①在串聯諧振或串聯諧振附近運行(從Fs大約為5ppm至200ppm).

②很好的短期穩定性.

③在1kHz至200MHz的任何頻率下工作.

④電路提供較大的輸出信號.

⑤以低功率驅動晶體.

⑥振蕩頻率幾乎對串聯.

電阻或并聯電容的微小變化不敏感.

電路配置:

①在大多數Pierce電路中,放大器僅由一個晶體管組成.可以對輸出進行緩沖,以提供數字邏輯兼容的輸出(TTL或HC-CMOS)

②Pierce放大器可以設計成具有CMOS,TTL和ECL中的數字邏輯元件;CMOS用于低頻,TTL用于中頻和ECL用于高頻.

晶體振蕩器的三態控制

大多數數字系統使用由兩個狀態級別0和1表示的二進制數字系統.在某些特殊應用中,需要第三狀態(HiImpedance輸出).TTL,HCMOS或HCMOS石英晶體振蕩器提供三態輸出或三態啟用/禁用功能.它的常見應用包括自動測試,總線接線數據傳輸.

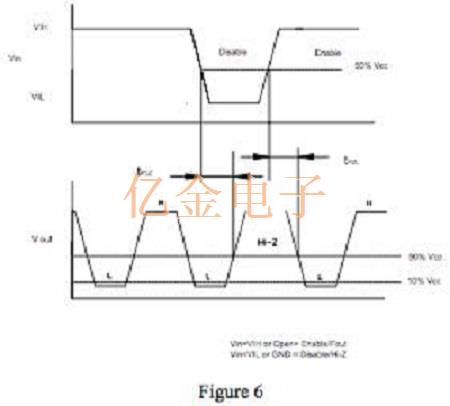

三種狀態分別為低,高和高阻抗(HiZ或浮動).高阻抗狀態下的輸出的行為就好像它與電路斷開連接一樣,只是漏電流很小.三態設備具有啟用/禁用輸入,通常在幾乎任何封裝的引腳1上.當使能為高電平或懸空時,器件振蕩(具有高和低輸出),并且當引腳1接地(邏輯”0”)時,器件進入高阻態.

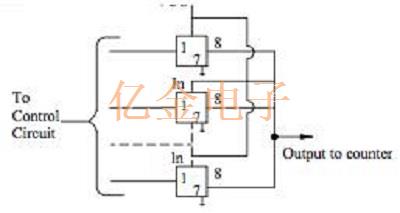

總線是一組常用的電線,通常用于數據傳輸.三態總線具有連接在一起的幾個三態輸出.通過控制電路,總線上除一個設備外的所有設備都具有處于高阻抗狀態的輸出.啟用其余設備,以高和低輸出驅動總線.

三態功能的其他應用是用于自動測試設備(ATE).幾個有源貼片晶振的輸出連接在一起.通過控制電路,除一個以外的所有振蕩器都具有處于高阻抗狀態的輸出.唯一選擇的振蕩器將從計數器中讀出其頻率.(圖5)

三態功能生效之前總會有一些延遲.在兩個轉換(禁用和啟用)上都會發生這種效果.從低電平到三態的輸出禁用時間為tPLZ,從低電平到三態的輸出使能時間為tPZL.(圖6)

CMOS

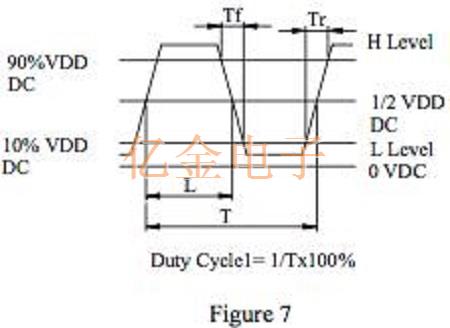

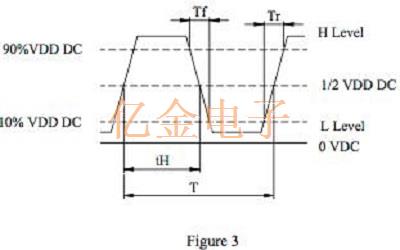

的上升和下降時間CMOS技術的上升和下降時間取決于其速度(CMOS,HCMOS,ACMOS,BICMOS),電源電壓,負載電容和負載配置.CMOS40000系列的典型上升和下降時間為30ns,HCMOS為6ns,而ACMOS(HCMOS,TTL兼容)的最大上升時間為3ns.典型的上升和下降時間在其波形電平的10%至90%之間測量.(見圖7)

ACMOS輸出端接技術

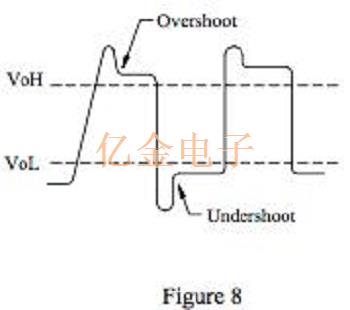

由于ACMOS(兼容HCMOS/TTL)器件的轉換時間很快,因此在測試或測量電氣性能特征時必須使用適當的端接技術.端接通常用于解決電壓反射問題,電壓反射問題實質上會導致時鐘波形出現階躍以及過沖和下沖.這可能導致錯誤的數據計時,以及更高的EMI和系統噪聲.

由于PC板上走線的長度及其負載配置,也需要端接.終止時鐘軌跡的一般方法有三種,這是將設備的輸出阻抗與線路阻抗相匹配的過程:

方法1:串聯端接在串聯端接中,將阻尼電阻放置在靠近時鐘信號源的位置.Rs的值必須滿足以下要求:Rs≥ZT–Ro.

方法2:上拉/下拉電阻在上拉/下拉終端中,組合的戴維南等效值等于走線的特性阻抗.這可能是最干凈的,不會產生反射,并降低了EMI.RT?ZT.

以上就是該文的全部內容,其中對石英振蕩器的應用技巧進行了詳細的說明,直至看完本文才知自己在這之前原來對有源晶振竟是僅知皮毛而已,本文對想要深入研究石英晶體振蕩器以及設計晶體振蕩器的朋友來說尤為珍貴,是一篇不可多得的技術性文章.

全球咨詢熱線

全球咨詢熱線 手機端

手機端

億金公眾號

億金公眾號 億金微信號

億金微信號