這樣設計PCB中晶振電路減少問題

不管是產品選型,還是電路設計,對于工程而言總會遇到大大小小的問題,那么如何更好的設計PCB呢?這樣設計PCB印刷電路板減少問題,在設計印刷電路板時,應考慮通過防止來抑制EMI水平負阻力下降.

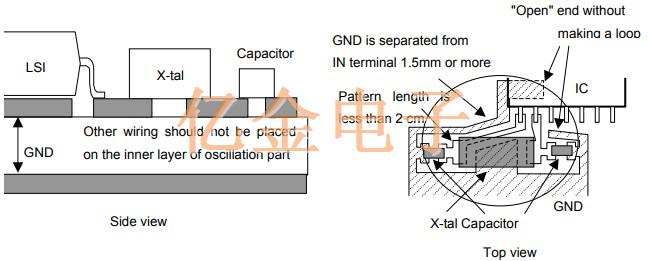

1.PCB上的圖案長度

為了防止布線的電感和雜散電容導致電氣特性的劣化,建議以最短的接線長度連接IC和電容器的石英晶體單元.這種模式長度應大約在2厘米以內,但長度越短,EMI輻射越小放置IC和晶體單元等元件不會成為問題.由于EMI主要來自于在逆變器的OUT側,該部分的圖形長度應該是晶體振蕩電路中最短的.而且,插件晶振不是優選的,因為它們成為EMI的來源.

2.晶體振蕩電路以外的圖案的影響

在設計多層PCB的情況下,重要的是不設計場地或其他信號模式在圖中圓圈部分的振蕩電路下,以防止負電阻減小,并獲得石英晶體振蕩器穩定的啟動特性.特別是,如果其他信號線位于靠近IN側的位置振蕩電路,振蕩波形將被調制引起噪聲,并在OUT側放大成為EMI的原因.由于晶體振蕩電路可能會停止啟動,如果IN端子的電壓和OUT端子在其他信號線的影響下變得相等,強烈建議不要設計它.還應該避免在振蕩電路附近的層上放置場地,因為它會減少負面阻力很大.

3.用場地屏蔽

當用場地屏蔽時,它將被放置在距離元件側最遠的層上,如圖所示左下圖.接地圖案不應放置在有源晶振,晶體振蕩電路中以避免負電阻降低,并且其他信號線也不應該放在這個部分,因為它會調制振蕩波形和通過降低負電阻來增加EMI.

如果元件上的有源晶振振蕩電路的接地圖案一側靠近信號線放置,EMI水平會降低,但如果放得太近,它會減少負阻,建議將其與振蕩電路的信號線分開0.5mm或更多.將接地圖案設置得太靠近振蕩電路的信號線是不利的,會降低負電阻,此外由于從IN輻射的EMI水平低,沒有必要這樣做.

全球咨詢熱線

全球咨詢熱線 手機端

手機端

億金公眾號

億金公眾號 億金微信號

億金微信號