使用HCMOS振蕩器的源阻抗端接建議

HCMOS 端接

通常,接收器的 HCMOS 兼容輸入顯示高輸入電阻與小引腳輸入電容并聯(lián)。接收器側(cè)不接受終端電阻,因為 HCMOS 接收器輸入需要軌到軌擺幅才能正確檢測“H”和“L”電平。在傳輸線的接收器端添加一個 termination resistor 會減小 clock 信號擺幅,并且接收器的 input 信號可能不再滿足所需的閾值電平。然而,接收器側(cè)傳輸線的準(zhǔn)開路端將導(dǎo)致信號反射,這些反射會傳回發(fā)射器,即振蕩器的緩沖器輸出級。這就是為什么建議在發(fā)射器側(cè)(即振蕩器的輸出)進(jìn)行阻抗匹配,以避免已經(jīng)在接收器側(cè)反射的脈沖進(jìn)一步反射。通過這種端接方法,波形不會退化,并且將滿足 HCMOS 接收器所需的標(biāo)準(zhǔn)波形。CMOS (HCMOS和LVCMOS)是適合低頻時鐘晶振 (通常低于250MHz)的方波數(shù)字輸出,可實現(xiàn)在時鐘輸出和芯片輸入之間直接連接。 在大多數(shù)情況下,可以使用低值串聯(lián)電阻器來有效減少信號反饋并保持可靠的信號完整性。

時鐘脈沖及其頻譜內(nèi)容

首先,重要的是要了解阻抗匹配的需求不取決于 clock frequency 本身,而是取決于沿 PCB 走線移動的信號邊沿的上升和下降時間。事實上,非常快的 rising 和 falling edges 將導(dǎo)致 oscillators clock frequency 倍數(shù)的高頻 spectral content 。這種高頻頻譜內(nèi)容是由高次諧波引起的,這些諧波包含在 clock output 信號的幾乎矩形波形中。

如果信號走線的長度接近 clock 信號的光譜內(nèi)容內(nèi)最高頻率的波長 λ,就會發(fā)生所謂的脈沖反射。由于高頻頻譜內(nèi)容取決于 clock 信號的上升和下降時間,因此可以根據(jù)振蕩器 clock output的指定上升和下降時間來估計 PCB 走線的臨界長度。CMOS (HCMOS和LVCMOS)通常為普通有源晶振輸出邏輯,包括壓控晶振(VCXO)及壓控溫補晶振 (VC-TCXO)等。

臨界波長 λ

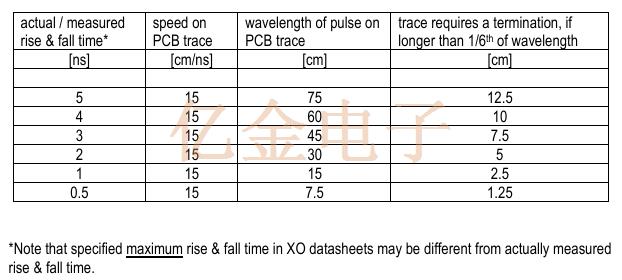

根據(jù)經(jīng)驗,我們可以說 signal trace 的臨界長度應(yīng)該比占 clock 信號上升沿或下降沿持續(xù)時間的諧波分量的波長 λ 短 6 倍。要計算波長 λ,我們必須考慮信號邊沿在傳輸線上的傳播速度。

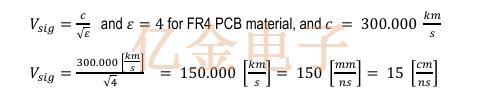

沿傳輸線的傳播速度由 PCB 基材決定。對于 εε=4 的 FR4 PCB 材料,傳播速度 VSig 可以估算如下:

對 PCB 設(shè)計的影響

假設(shè)信號軌跡的長度短于在該軌跡上傳播的快速脈沖波長的1/6,那么如果上升和下降時間在電壓擺動的10%~90%給出,我們可以估計軌跡的關(guān)鍵長度與時鐘信號的上升和下降時間的關(guān)系。如果上升和下降時間規(guī)定為電壓擺幅的 20% 和 80%,則基于 1/4 波長的計算是可以接受的。

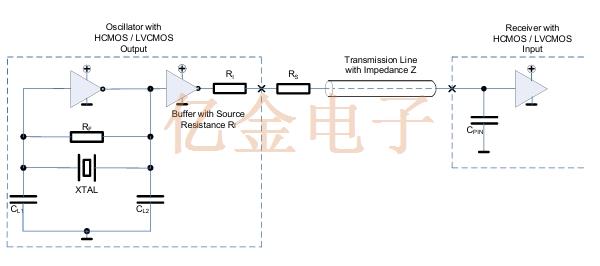

源阻抗終端

由于不允許在接收器端接,因此建議在石英晶體振蕩器輸出和傳輸線之間進(jìn)行阻抗匹配,以避免反射在 PCB 走線的兩個方向上傳播。假設(shè)振蕩器的輸出具有源阻抗 RI,并且傳輸線具有高于 RI 的特性阻抗 Z,則應(yīng)增加一個串聯(lián)電阻 RS。為了實現(xiàn)最佳阻抗匹配,RI 和 RS 之和應(yīng)等于特性阻抗 Z。RS 的最佳值可以通過實驗確定,尤其是在 PCB 走線的阻抗 Z 未知的情況下。

如果使用具有 HCMOS 輸出的32.768K振蕩器,則應(yīng)將串聯(lián)電阻 RS 放置在非常靠近振蕩器輸出的位置。源阻抗 RI 和串聯(lián)電阻 RS 之和應(yīng)等于傳輸線的阻抗 Z。

這種推薦配置的目的是避免在傳輸線的接收器端反射的脈沖進(jìn)一步反射。通常,不建議在接收器側(cè)使用 termination resistor,因為它們會降低 clock 信號的電壓擺幅,并且可能無法再達(dá)到接收器側(cè)所需的閾值電平。

全球咨詢熱線

全球咨詢熱線 手機端

手機端

億金公眾號

億金公眾號 億金微信號

億金微信號