集成電路系統的平衡和低阻抗晶振的使用

隨著專用集成電路的普及,其性能和速度也有了更高的限制,同時驅動多個設備變得更加困難,這是高性能系統目前的局限,所以我們需要一個強大的時鐘晶振源來增強使用空間.但是由于快速邊沿速率,系統中部署的較高頻率導致長PCB跡線表現得像傳輸線.維護平衡系統需要適當的終止技術來實現應用程序中的跟蹤路由.

通常,大多數時鐘晶振具有低阻抗輸出。當這些器件用于驅動具有大阻抗的負載時,存在阻抗不匹配。根據應用條件,此阻抗不匹配會導致負載產生電壓反射,從而在時鐘波形,振鈴以及過沖和下沖中產生步進。這可能通過降低負載處的時鐘信號,錯誤的數據時鐘和產生更高的系統噪聲而導致系統性能不佳。

為了減少電壓反射,需要正確終止信號跡線。適當終止的設計考慮因素可歸納為兩個陳述:

1.將負載阻抗匹配到線路阻抗

2.將源阻抗與線路阻抗進行匹配

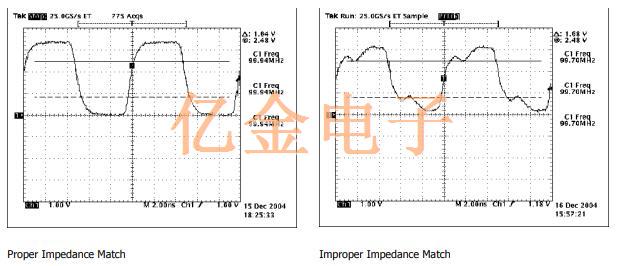

對于大多數設計,第一種說法是首選方法,因為它消除了返回時鐘源的反射。這樣可以減少噪音,電磁干擾(EMI)和射頻干擾(RFI)。下圖顯示了阻抗不匹配對較高頻率時鐘源的影響。

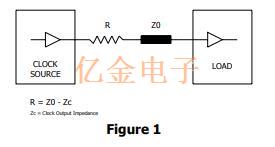

如上所述,為了減少電壓反射,必須正確地終止跡線。傳輸線的四種基本端接技術是串聯,并聯,戴維南和AC。串聯終端消除了時鐘源的反射,四腳有源石英晶振有助于保持信號質量。這最適合驅動少量負載的TTL器件,因為時鐘輸出阻抗小于傳輸線特性阻抗。圖1顯示了一系列終端。電阻盡可能靠近時鐘源放置。R的典型設計值為10Ω至75Ω。

R的值可以大于阻抗差,以便產生稍微過阻尼的狀態并且仍然消除來自時鐘源的反射。

系列終端的主要優點是:

1.簡單,只需要一個電阻器

2.功耗低

3.驅動高容性負載時產生電流限制;這還可以通過減少接地反彈來改善抖動性能。

系列終止的主要缺點是:

1.增加負載信號的上升和下降時間;在某些高速應用中,這可能是不可接受的

2.無法驅動多個負載

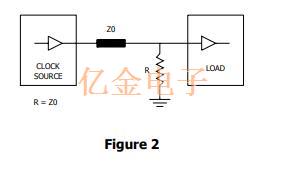

接下來的兩種終端技術可提供更清晰的時鐘信號,并消除負載端的反射。這些終端應盡可能靠近負載放置。圖2描繪了并行終端。并聯終端消耗的功率最大,不建議用于低功率應用。高精度貼片晶振也可能改變占空比,因為下降沿將比上升沿更快。它比串聯終端具有一個優點,即上升和下降時間的延遲大約是一半。

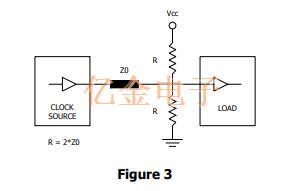

如圖3所示,戴維南終端將比并聯終端消耗更少的功率,并且通常用于PECL應用的50Ω線路匹配至關重要。R的總值等于傳輸線的特征阻抗。如果需要過阻尼條件,則R的總值可略小于特征阻抗。戴維南終端的主要缺點是每條線路需要兩個電阻器,并且在終端附近需要兩個有源晶振。不建議將此端接用于TTL或CMOS電路。

時鐘晶振作為抵抗組輸出的選擇,維護系統平衡是主要任務之一,提供更清晰的時鐘信號正是需要解決的問題,生成可靠的應用程序可以最大限度的降低時鐘信號的條件,來保持系統性能的穩定

全球咨詢熱線

全球咨詢熱線 手機端

手機端

億金公眾號

億金公眾號 億金微信號

億金微信號